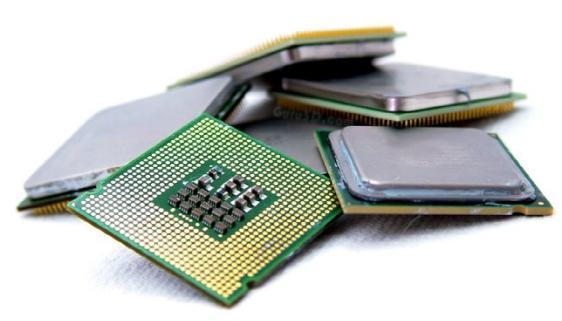

半导体制程工艺对各类芯片来说意义非凡,在一般情况下更先进、密度更高的制程工艺可以让芯片获得更好的能耗比,同时发热量等一些物理特性也会得到改善。按官方数字来看,目前7纳米工艺应该是世界上最先进的制程功能,在消费电子领域使用7纳米芯片打造的芯片都拥有令人刮目相看的表现,但科技的进步远不限于此。

不久前台积电宣布正在推动5纳米制程工艺的研究计划,并计划于明年正式投产。外界预计5纳米工艺将用于苹果A14芯片上,而今年的A13芯片将继续使用7纳米工艺,但这是更先进的7纳米 EUV工艺,性能表现要更加出色。

显然先进的工艺会带来高昂的成本,除了苹果A系列、华为9系和高通骁龙8系旗舰芯片外,这些厂商的中低端芯片显然不会采用如此高成本的制程工艺来加工芯片。这时候,推出一个性能稍弱但依然出色的加工工艺就很有必要。

今天早些时候,台积电宣布推出过渡工艺6纳米,该工艺最快或于2020年第一季度试产。官方预计6纳米工艺在逻辑密度上要比现有7纳米工艺提升18%,转化到具体产品中性能应该会有一定提升。

相比5纳米工艺,6纳米工艺更像是7纳米工艺的“换皮”版本,也就是一个小幅度升级版。6纳米工艺更适合用于一些中端或者次旗舰芯片上,这种策略实际上早已有先例可鉴,不算罕见。目前市场上除了顶尖的7纳米工艺外,也存在8纳米工艺;在10纳米时代也存在11纳米、12纳米,可想而知像芯片一样,工艺同样需要次一级旗舰的存在。

未来6纳米工艺可能会用于高通骁龙7系次旗舰芯片或者部分联发科芯片上,这些芯片的性能表现虽然不如5纳米芯片那般极致,但提升幅度也不小。随着芯片逻辑密度日渐逼近物理极限,未来想要继续突破恐怕已经不太容易。同时摩尔定律也早已失效,制程工艺到了5纳米级别看来会停滞很长一段时间。

关键词:

责任编辑:Rex_02